Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

#### **Features**

- Internal Op-Amp -3dB Band-Width: 60MHz (90MHz with FST\_EN), Av = 1

- Slew Rate: 70V/µS (120V/µS with FST\_EN)

- Wide Supply Range: 2.5V to 12V

- Output Current: 20mA (45mA with FST\_EN)

- Four Separated Output Array

- Output Swings Rail-to-Rail

- Output Offset Voltage, Rail-to-Rail: 5mV Max

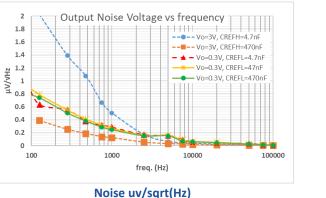

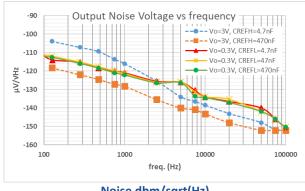

- Low Output Noise: 20µvrms (10Hz to 100kHz)

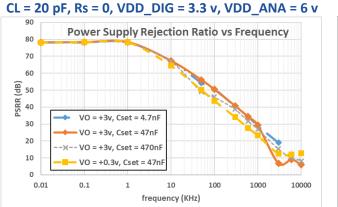

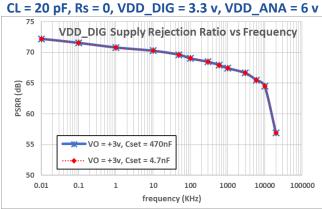

- Power Supply Rejection: 75dB Typ.

- Programmable Soft-Start

- Operating Temperature Range: –40°C to 125°C

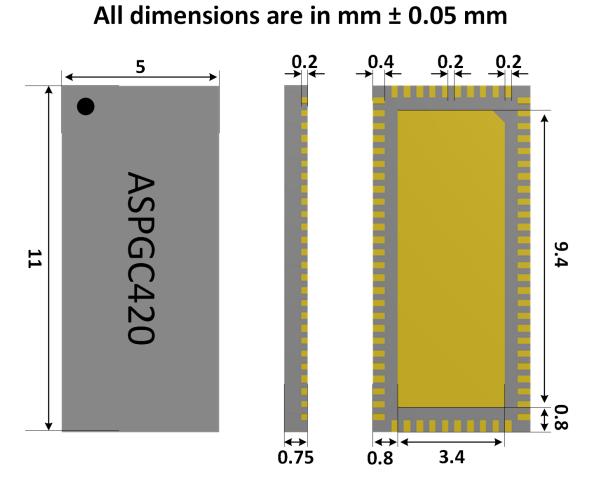

- Low Profile (5mm x 11mm x 0.75mm) QFN Package

#### **Applications**

- Power Management unit

- RF Amplifier Gate Control and Monitoring

- RF Transceivers

#### Description

The ASPGC4X20 is a quad negative gate control and monitor with up to 120 V/ $\mu$ S output slew rate. The outputs have been driven with four unity- gain amplifiers with a gain-bandwidth of 60MHz and a 20mA (40mA with FST EN) output current fit the requirements of high-performance RF bias boards. The ASPGC4X20 has a digital positive SELECT input and quad rail to rail outputs that swing within 100mV of GND and 300mV of VDD ANA rail to maximize the signal dynamic range in low voltage applications. The ASPGC4X20 has low output RMS noise and precision output voltage levels that are adjusted with only two resistors. It has four precision monitoring blocks with adjustable power good range and four output flags. The ASPGC4X20 maintains its performance with a VDD ANA voltage from 3V to 12V and a VDD DIG voltage from 2V to 5V. The Input digital SELECT levels are GND and VDD\_DIG and the output voltage and monitoring levels can be set between GND and VDD ANA.

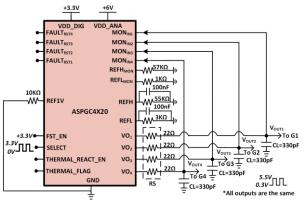

## **Typical Application**

#### Quadrative Gate Control and monitoring

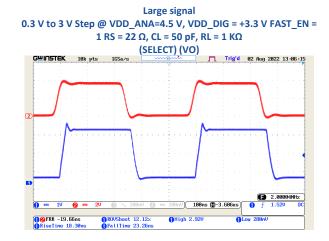

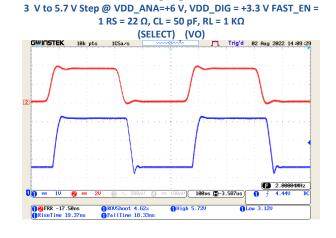

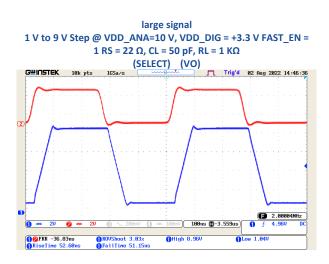

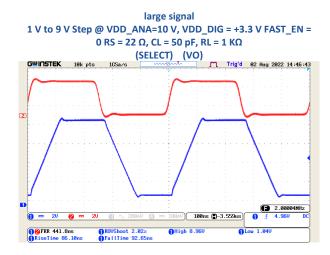

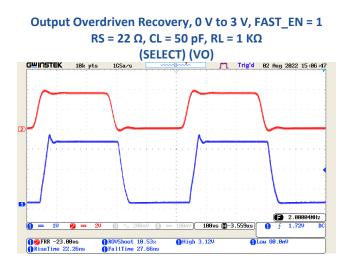

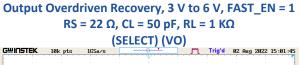

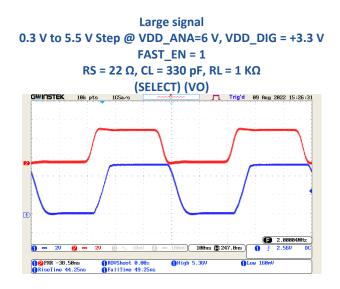

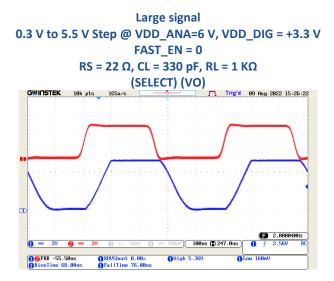

Large signal

0.3 V to 5.5 V Step @ VDD\_ANA=6 V, VDD\_DIG = +3.3 V FAST\_EN = 1 RS = 22 Ω, CL = 330 pF, RL = 1 KΩ

ab<u>ba-se</u>mj

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

#### **Absolute Maximum Rating**

| VDD_ANA                       | 0.5 V to 13 V           |

|-------------------------------|-------------------------|

| VDD_DIG                       | 0.5 V to 5.5 V          |

| GND                           | 0 V                     |

| FAULT_RSTx                    | 0.5 V to VDD_DIG +0.5 V |

| SELECT                        | 0.5 V to VDD_DIG +0.5 V |

| FST_EN                        | 0.5 V to VDD_DIG +0.5 V |

| THERMAL_REACT_EN              | 0.5 V to VDD_DIG +0.5 V |

| THERMAL_FLAG                  | 0.5 V to VDD_DIG +0.5 V |

| VOx , MON_INx                 | 0.5 V to VDD_ANA+0.5 V  |

| REFH, REFL                    | 0.5 V to VDD_ANA+0.5 V  |

| REFH_MON, REFL_MON            | 0.5 V to VDD_ANA+0.5 V  |

| REF1V                         | 0.5 V to 5 V            |

| Maximum Junction Temperature. | 250 °C                  |

#### **Recommended Pin Voltage Range**

| VDD_ANA                       | 3 V to 13 V                |

|-------------------------------|----------------------------|

| VDD_DIG                       | 2.5 V to 5.5 V             |

| GND                           | 0 V                        |

| FAULT_RSTx                    | Digital OUT (0 to VDD_DIG) |

| SELECT                        | Digital IN (0 to VDD_DIG)  |

| FAST_EN                       | Digital IN (0 to VDD_DIG)  |

| THERMAL_REACT_EN              | Digital IN (0 to VDD_DIG)  |

| THERMAL_FLAG                  | Digital OUT (0 to VDD_DIG) |

| VOx                           | +0.1 V to VDD_ANA -0.3 V   |

| MON_INx                       | +0.1 V to VDD_ANA -0.3 V   |

| REFH, REFL                    | +0.1 V to VDD_ANA -0.3 V   |

| REFH_MON, REFL_MON            | 0 V to VDD_ANA -0.3 V      |

| REF1V                         | Analog OUT (+1 V)          |

| Maximum Junction Temperature. | 150 °C                     |

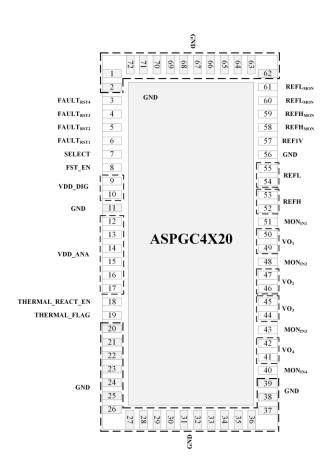

### **Pin Configuration**

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

| Symbol                                                | Parameter                      | $\frac{R_{REFH} = 33.8 \text{ K}\Omega, R_{REFL} = 3 \text{ K}\Omega, R_{REF1V} = 10}{\text{Conditions}}$ | MIN      | ТҮР       | MAX | UNITS             |

|-------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|----------|-----------|-----|-------------------|

| VREF <sub>1V</sub>                                    |                                | RREF1V=10K                                                                                                |          | 1.05      |     | V                 |

| VREFH                                                 |                                |                                                                                                           |          | 3.57      |     | V                 |

| VREF∟                                                 |                                |                                                                                                           |          | 0.313     |     | V                 |

| VREFHMON                                              |                                |                                                                                                           |          | 4.07      |     | V                 |

|                                                       |                                |                                                                                                           |          | 0.21      |     | V                 |

| IREF∟                                                 |                                |                                                                                                           |          | 104.3     |     | μA                |

| IREFH                                                 |                                |                                                                                                           |          | 105.6     |     | μΑ                |

| IREFLMON                                              |                                |                                                                                                           |          | 105       |     | μΑ                |

| IREFHMON                                              |                                |                                                                                                           |          | 104.1     |     | μΑ                |

|                                                       |                                | Select = High                                                                                             |          | 3.59      |     | <u>بر مر</u><br>۷ |

| Vo                                                    |                                | Select = Low                                                                                              |          | 0.32      |     | v                 |

|                                                       |                                | Select = High                                                                                             |          | 100       |     | uA                |

| IIN-SELECT                                            | Select = Low                   |                                                                                                           | 0        |           | uA  |                   |

| V <sub>OL</sub> Output Voltage<br>Lower-Level Swing   | No Load                        |                                                                                                           | 0.1      |           | V   |                   |

|                                                       | $I_{Load} = \pm 20 \text{mA}$  |                                                                                                           | 0.1      |           | V   |                   |

|                                                       | No Load                        |                                                                                                           | 4.15     |           |     |                   |

| V <sub>он</sub>                                       |                                | $I_{Load} = \pm 20 mA$                                                                                    |          | 4.15      |     | V                 |

|                                                       |                                | to GND, FST_EN=Low                                                                                        |          | 28        |     |                   |

| L                                                     | Output Short                   | to VDD_ANA , FST_EN= Low                                                                                  |          | 34        |     | mA                |

| lsн                                                   | Circuit                        | to GND, FST_EN=High                                                                                       |          | 48        |     |                   |

|                                                       | to VDD_ANA , FST_EN= High      |                                                                                                           | 58       |           |     |                   |

| IDD-Dig                                               | Digital Supply<br>Current      | No Load                                                                                                   |          | 1         |     | mA                |

| l <sub>vss</sub>                                      | Analog Supply                  | No Load, FST_EN=Low                                                                                       |          | 37        |     | mA                |

| 1055                                                  | Current                        | No Load, FST_EN=High                                                                                      |          | 58        |     | IIIA              |

| VSELECTH                                              | Select Digital High<br>Level   |                                                                                                           |          | 2.2       |     | V                 |

| Vselectl                                              | Select Digital Low<br>Level    |                                                                                                           |          | 1.48      |     | V                 |

|                                                       | Coloct command                 | $FST_EN = High, C_L = 330pF$                                                                              |          | 10        |     | ns                |

| toruvou                                               | Select command                 | FST_EN = Low, CL = 330pF                                                                                  |          | 15        |     | ns                |

| tsel-volh                                             | delay to output V <sub>0</sub> | FST_EN = High, C <sub>L</sub> = 20pF                                                                      |          | 4         |     | ns                |

| 10% (Low to High)                                     | FST_EN = Low, CL = 20pF        |                                                                                                           | 6        |           | ns  |                   |

|                                                       | Select command                 | FST_EN = High, CL = 330pF                                                                                 |          | 23        |     | ns                |

| tsel-vohl                                             | delay to output Vo             | $FST_EN = Low, C_L = 330pF$                                                                               |          | 25        |     | ns                |

| SLL-VUIL                                              | 10% (High to Low)              | FST_EN = High, CL = 20pF                                                                                  |          | 17        |     | ns                |

|                                                       | $FST_EN = Low, C_L = 20pF$     |                                                                                                           | 21       | ↓         | ns  |                   |

|                                                       | <b>Rising time</b>             | FST_EN = High, CL = 330pF                                                                                 |          | 39        |     | ns                |

| t <sub>R</sub>                                        | 0.5V to 4V                     | $FST_EN = Low, C_L = 330pF$                                                                               |          | 59        |     | ns                |

|                                                       | 10% to 90%                     | $FST_EN = High, C_L = 20pF$                                                                               |          | 27        |     | ns                |

|                                                       |                                | $FST_EN = Low, C_L = 20pF$                                                                                |          | 47        |     | ns                |

| Falling time   t <sub>F</sub> 4V to 0.5V   90% to 10% | FST_EN = High, CL = 330pF      |                                                                                                           | 40       |           | ns  |                   |

|                                                       | $FST_EN = Low, C_L = 330pF$    |                                                                                                           | 61       |           | ns  |                   |

|                                                       | $FST\_EN = High, C_L = 20pF$   |                                                                                                           | 30       |           | ns  |                   |

|                                                       | $FST_EN = Low, C_L = 20pF$     |                                                                                                           | 50       | +         | ns  |                   |

| Slew rate Slew rate                                   | $FST_EN = High, C_L = 330pF$   |                                                                                                           | 90<br>60 |           |     |                   |

|                                                       | Slew rate                      | $FST_EN = Low, C_L = 330pF$                                                                               |          | 60<br>115 |     | V/µs              |

|                                                       |                                | $FST_EN = High, C_L = 20pF$<br>$FST_EN = Low, C_L = 20pF$                                                 |          | 115<br>70 |     |                   |

www.abba-semi.com

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

| t <sub>DPG</sub>        |                                                                                      | Power good<br>Power Bad | 82<br>1000 | ms<br>ns |

|-------------------------|--------------------------------------------------------------------------------------|-------------------------|------------|----------|

| VOS <sub>MH</sub>       | REFH/L <sub>MON</sub> to<br>MON <sub>IN</sub> offset<br>voltage to remove<br>PG flag |                         | ±1.5       | mV       |

| MONHYST                 |                                                                                      |                         | 28         | mV       |

| PSRR <sub>VDD_ANA</sub> |                                                                                      | VSS = 4V , 12V          | 81         | dB       |

| PSRR <sub>DIG</sub>     |                                                                                      | VDD_DIG = 2V , 5V       | 95         | dB       |

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

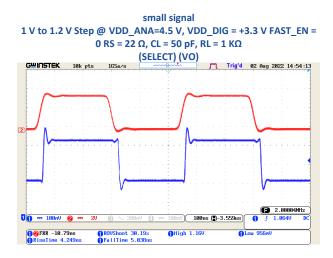

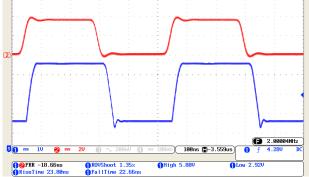

#### Gate Control Typical Performance Characteristics TA = 25° unless otherwise noted

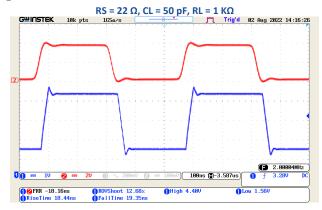

Large signal +1.5 V to +4.5 V Step @ VDD\_ANA=+6 V, VDD\_DIG = +3.3 V FAST\_EN = 1

Large signal

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

#### **Pin Functions**

**GND:** Ground. Tie these pads to local ground plate on PCB. To ensure proper electrical and Thermal performance connect all pins with wide polygon to ground.

**VDD\_ANA:** The VDD\_ANA pin supplies current to the ASPGC4X20's internal Output Buffer and to the internal Reference block. This pin must be locally bypassed with an external, low ESR capacitor of at least  $4.7\mu$ F. The VDD\_ANA pin voltage level is positive and should be set between +3V to +12V for best chip performance.

**VDD\_DIG:** The VDD\_DIG pin supplies current to the ASPGC4X20's internal SELECT input section and to the internal monitoring block. This pin must be locally bypassed with an external, low ESR capacitor of at least  $1\mu$ F. The VDD\_DIG pin voltage level is positive and should be set between 2.5V to 5V for best chip performance.

**REFL**<sub>MON</sub>, **REFH**<sub>MON</sub>: ASPGC4X20 Monitoring Reference pads. For  $R_{REF1V}$  equal to 10Kohm, a fixed current of 101µA flows out from these pins through a single external resistor ( $R_{HMON}$ ,  $R_{LMON}$ ) connected between ground and each pad, which sets a positive voltage on each pad to program the monitoring reference levels. For correct function of monitoring block, the value of  $R_{HMON}$  must SELECTed greater than  $R_{LMON}$  (REFL<sub>MON</sub> pin voltage must be lower than REFH<sub>MON</sub>). In order to reject high frequency noise a parallel capacitor ( $C_{HMON}$ and  $C_{LMON}$ ) can be used with  $R_{HMON}$  and  $R_{LMON}$ . Do not use more than 10nF for  $C_{HMON}$  and  $C_{LMON}$ .

**REFL, REFH:** ASPGC4X20 Output voltage levels Reference pads. For  $R_{REF1V}$  equal to 10Kohm, a fixed current of 101µA flows out from these pins through a single external resistor ( $R_{REFH}$ ,  $R_{REFL}$ ) connected between ground and each pad, which sets a positive voltage on each pad to program the output voltage reference levels. The value of  $R_{REFH}$ must be selected greater than  $R_{REFL}$  (REFL pin voltage must be lower than REFH). In order to reject high frequency noise a parallel capacitor (CREFH and CREFL) can be used with RHMON and RLMON. Do not use more than  $1\mu$ F for CREFH and CREFL.

**REF1V:** Current Reference pad. A 1.01V is internally applied between this pad and GND. Connect a 1% 10K resistor between this pad and GND to set a 101uA reference current that flows out from REFL, REFH, REFH<sub>MON</sub> and REFL<sub>MON</sub> pads.

**FAULT<sub>RSTX</sub>:** Monitoring digital output flag. The pad output High level voltage is VDD\_DIG and Low level voltage is 0V. The pin output level is High if  $MON_{INX}$  voltage is between REFL<sub>MON</sub> and REFH<sub>MON</sub> and is Low otherwise. High to low transition of this pad happens immediately (300ns delay) and at  $MON_{INX}$  <REFL<sub>MON</sub> or >REFH<sub>MON</sub> and low to high transition happens with a typical 82ms delay after

$REFLMON+25mV < MON_{INX} < REFH_{MON}-25mV$

**MON**<sub>INX</sub>: Monitoring input. This pad should be connected in remote sense condition (without current) to a negative voltage relative to ground. The function of monitoring is explained above. Two protection diode is internally connected between this pad and VDD\_ANA/GND pads so the applied voltage on MONINX pad must be between VDD\_ANA and GND.

**VO<sub>x</sub>:** ASPGC4X20 output pad. This pad is internally driven by a unity gain amplifier with 60MHz bandwidth, a 70V/us (Up to 120V/us by FST\_EN) slew rate and a 70deg phase margin at 20pF capacitive load. The maximum output capacitive load is 30pF for stability. For more capacitive loads connect a 22 $\Omega$  series resistor (RS) in the output. The output current limit is 23mA DC (up to 45mA with FST\_EN) and 500mA peak (less than 200ns). This pad voltage levels is set by REFH and REFL pads. The VO<sub>x</sub> = V<sub>REFL</sub> if SELECT=Low and VO<sub>x</sub>=V<sub>REFH</sub> if SELECT=High.

**SELECT:** ASPGC4X20 digital input. The pad input High level voltage is VDD\_DIG and Low level is 0V. This pad sets VO<sub>x</sub> voltage level on REFH and REFL voltage. The VO<sub>x</sub> =  $V_{REFL}$  if SELECT=Low and VO<sub>x</sub>=V<sub>REFH</sub> if SELECT=High. SELECT pad is

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

internally protected for input voltages above VDD\_DIG and below 0V. Minimum input pulse width is 60ns. This pad is internally pulled down.

**FST\_EN:** Fast operation mode enable pad. In fast operation mode the supply current of the ASPGC4X20 increases to about 2 time more than typical usage continually so the outputs slew rate and bandwidth increases to 120V/us and 90MHz respectively. The current usage is doubled in Fast mode. Fast mode operation is recommended if extra power consumption is ignorable in the system. This pad is internally pulled down.

**THERMAL\_FLAG:** Over temperature output digital flag pad. The pad output Low and High voltage levels are 0V and VDD\_DIG, respectively. The output is LOW when the temperature is below 180°C and is high otherwise.

**THERMAL\_REACT\_EN:** Over temperature (OT) reaction enable pad. This pad is a pulled up digital input. Tie it to GND to disable the OT reaction mode and leave it to enable that. In OT reaction mode the supply current usage and outputs current limit level is decrease by 80% while the chip internal temperature is increased above 180°C.

Quadruple, Positive Voltage Low noise, 120V/µs, Rail-to-Rail Adjustable Output RF Amplifier Gate Bias Control & Monitoring

### **Application Information**

#### **PCB Layout**

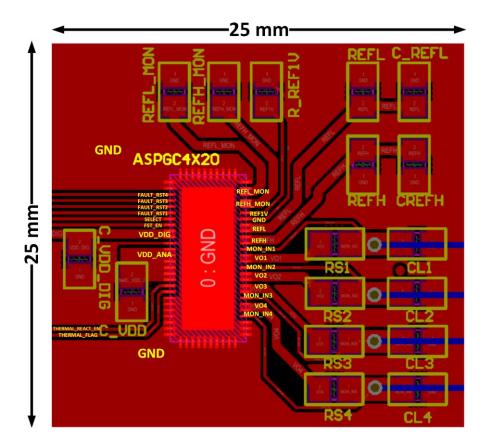

The ASPGC4X20 includes quad negative gate control and monitor. Even with the high level of integration, you may fail to achieve specified operation with a haphazard or poor layout. See Figure 3 for a suggested layout. Ensure that the grounding and heat sinking are acceptable. A few rules to keep in mind are:

- **1.** Place the  $R_{REFL}$ ,  $R_{REFH}$ ,  $R_{REFHMON}$ ,  $R_{REFLMON}$  and  $R_{REF1V}$  resistors as close as possible to their respective pins.

- **2.** Place the  $C_{REFH}$  and  $C_{REFL}$  capacitors as close as possible to their respective resistors.

- **3.** Place the RS resistors as close as possible to their respective pins.

- Connect all of the GND connections to as large a copper pour or plane area as possible on the top layer. Avoid breaking the ground connection between the external components and the ASPGC4X20.

- **5.** CL capacitors can be placed far from the ASPGC4X20 if RS resistors have been used.

- 6. It is recommended to connect MON\_IN track without DC current path to monitor the consumer voltage level.

- 7. Use vias to connect the GND copper area to the board's internal ground plane. Liberally distribute these GND vias to provide both a good ground connection and thermal path to the internal planes of the printed circuit board.

72 pin QFN Package