### 40 V, 2 A EM Compliant Switching Regulator with 2-Output Configurable LDO

#### **Features**

- Step-Down Switch Mode Power Supply

- Wide Input Voltage Range: 8V to 40V

- 2 A Buck Output Current

- 2V to 12.5V Output Voltage

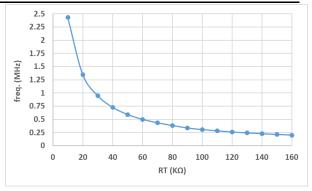

- Selectable Switching Frequency: 0.2 MHz to 2.5 MHz

- Adjustable 10% Accurate Current Limit

- Configurable Output LDO Array

- Two 1 A Parallelable Outputs

- Outputs Adjustable From 0 V to 12 V

- Low Output Noise: 6µvrms (10Hz to 100kHz)

- Programmable Soft-Start

### **Applications**

- Automotive Battery Regulation

- FPGA, DSP, ASIC and Microprocessor Supplies

- Servers and Storage Devices

- RF Transceivers

## **Description**

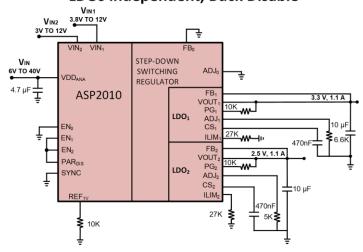

The ASP2010 is a 40 V, 2 A step-down High-Side switch and regulator controller chip with a 2-output configurable LDO array. Operating over an input voltage range of 8 V to 40 V, the ASP2010 buck regulator supports an output voltage range of 2V to 12.5 V and wide selectable switching frequency range of 200 kHz to 2.5 MHz each ADJ by a single resistor. The buck regulator has synchronization possibility and generates low switching noise. Following the buck regulator is a couple of 1 A linear regulators whose outputs may be connected in parallel to accommodate a wide variety of load combinations.

The ASP2010 is packaged in thermally enhanced QFN package and has high efficiency which makes it a good solution for high density power management units.

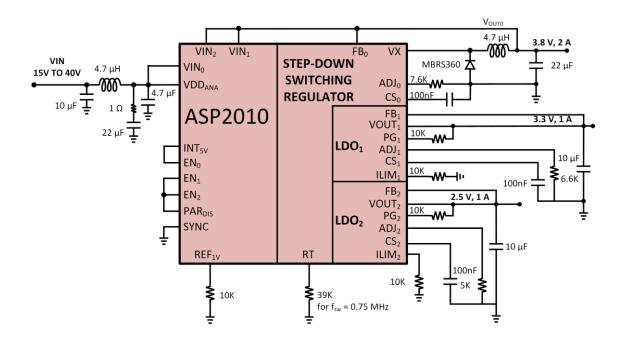

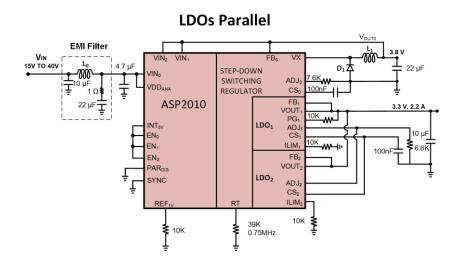

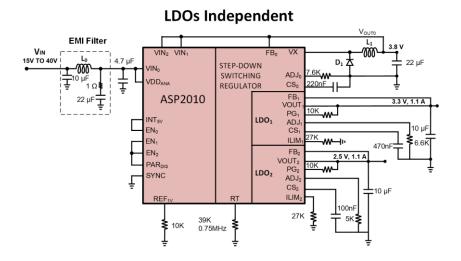

## **Typical Application**

## **Dual 1A Regulated Outputs**

## **Absolute Maximum Rating**

| VIN <sub>0</sub> , VDD <sub>ANA</sub> , VX                                                                                      | 45 V   |

|---------------------------------------------------------------------------------------------------------------------------------|--------|

| EN <sub>0</sub> , INT_5V, EN <sub>1</sub> , EN <sub>2</sub> , PAR <sub>DIS</sub> , TH_SHTD                                      | 5.5 V  |

| SYNC, RT, ADJ <sub>0</sub> , ADJ <sub>1</sub> , ADJ <sub>2</sub> , REF <sub>1V</sub>                                            | 5.5 V  |

| PG <sub>0</sub> , PG <sub>1</sub> , PG <sub>2</sub> , ILIM <sub>1</sub> , ILIM <sub>2</sub> , FB <sub>0</sub> , CS <sub>0</sub> | 5.5 V  |

| SET, STRB, DIN, CLK                                                                                                             | 5.5V   |

| VIN <sub>1</sub> , VIN <sub>2</sub>                                                                                             | 13 V   |

| FB <sub>1</sub> , FB <sub>2</sub> , CS <sub>1</sub> , CS <sub>2</sub>                                                           | 13 V   |

| VOUT <sub>1</sub> , VOUT <sub>2</sub>                                                                                           | 13 V   |

| Maximum Junction Temperature                                                                                                    | 200 °C |

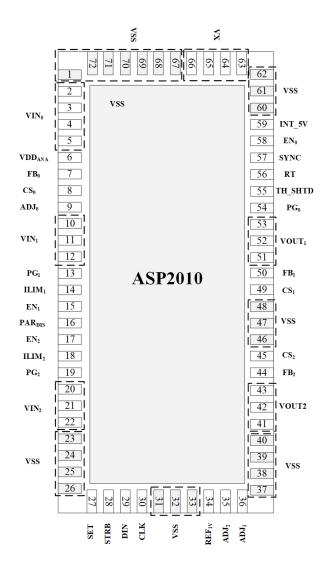

## **Pin Configuration**

# **ASP2010**

## 40 V, 2 A EM Compliant Switching Regulator with 2-Output Configurable LDO

| arameter                                               | Conditions                                                                                               | MIN  | TYP         | MAX         | UNITS      |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|-------------|-------------|------------|

| Buck Regulator                                         |                                                                                                          |      |             |             |            |

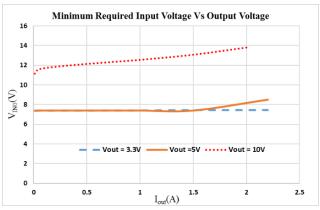

| Minimum Required VIN₀ Input<br>Voltage to run          | VOUT = 5V                                                                                                | 7.4  |             | 8.5         | V          |

| VOUT₀ DC Voltage                                       | 0 A < $I_{out}$ < 2 A ADJ <sub>0</sub> = 4 kΩ<br>0 A < $I_{out}$ < 2 A ADJ <sub>0</sub> = 24 kΩ          |      | 2<br>12     |             | V<br>V     |

| Quiescent Current into VIN <sub>0</sub>                | $EN_0$ , $EN_1$ , $EN_2 = 0$                                                                             |      | 5           |             | mA         |

| VOUT₀ Line Regulation                                  | 8V < VIN <sub>0</sub> < 40V, I <sub>out</sub> = 2 A                                                      |      | ±0.5        |             | %          |

| VOUT₀ Load Regulation                                  | VIN <sub>0</sub> = 28 V, 0 A < I <sub>out</sub> < 2 A                                                    |      | ±1          |             | %          |

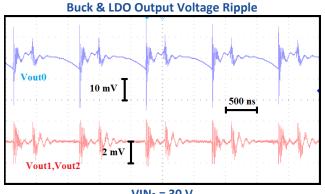

| VOUT₀ RMS Voltage Ripple                               | VIN <sub>0</sub> = 28 V, VOUT <sub>0</sub> = 5 V, 0 A < I <sub>out</sub> <2 A                            |      | 7.4         |             | mV         |

| VOUT <sub>0</sub> RMS Output Noise                     | VOUT <sub>0</sub> = 5 V, I <sub>Load</sub> = 1 A, CS <sub>0</sub> = 10 nF<br>10Hz to 100 kHz             |      | 198         |             | μV         |

| VOUT₀ RMS Output Noise                                 | VOUT <sub>0</sub> = 5 V, I <sub>Load</sub> = 1 A, CS <sub>0</sub> = 470 nF<br>10Hz to 100 kHz            |      | 140         |             | μV         |

| Switching Frequency                                    | RT = 28 kΩ<br>RT = 160 kΩ                                                                                |      | 1000<br>200 |             | kHz<br>kHz |

| EN₀ Threshold Voltage                                  | OFF                                                                                                      |      |             | 0.5         | V          |

| EN <sub>0</sub> Threshold Voltage                      | ON                                                                                                       | 1    |             |             | V          |

| ADJ <sub>0</sub> Pin Current                           | $R_{ref} = 10 \text{ k}\Omega$                                                                           | 98   | 100         | 102         | μΑ         |

| RT Pin Voltage                                         |                                                                                                          | 0.99 | 1.01        | 1.03        | V          |

| SYNC Input Low Threshold                               |                                                                                                          |      |             | 0.5         | V          |

| SYNC Input High Threshold                              |                                                                                                          | 1    |             |             | V          |

| LDO Array                                              |                                                                                                          |      |             |             |            |

| ADJ <sub>1</sub> , ADJ <sub>2</sub> Pin Current        | $R_{ref} = 10 \text{ k}\Omega$                                                                           | 98   | 100         | 102         | μΑ         |

| REF1V Pin Voltage                                      |                                                                                                          | 0.99 | 1.01        | 1.03        | V          |

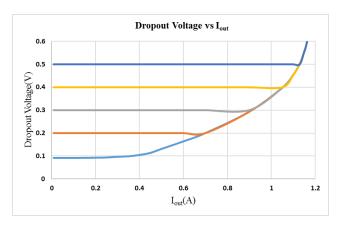

| LDO1, LDO2 Dropout Voltage                             | Load = 100 mA<br>Load = 700 mA                                                                           |      |             | 0.09<br>0.2 | V<br>V     |

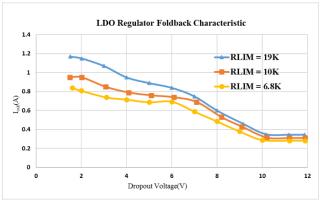

| LDO1, LDO2 Maximum Dropout<br>Voltage                  | R <sub>LIM</sub> = 19k, I <sub>Load</sub> = 390 mA<br>R <sub>LIM</sub> = 19k, I <sub>Load</sub> = 600 mA |      |             | 9.5<br>8    | V<br>V     |

| voitage                                                | R <sub>LIM</sub> = 19k, I <sub>Load</sub> = 800 mA                                                       |      |             | 6.5         | V          |

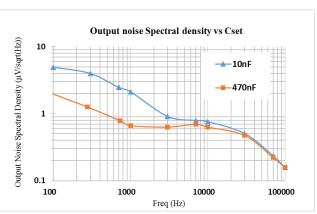

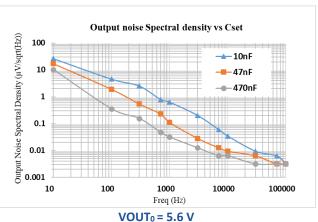

| VOUT <sub>1</sub> , VOUT <sub>2</sub> RMS Output Noise | VOUT <sub>1,2</sub> = 5 V, I <sub>Load</sub> = 400 mA, 100 Hz to<br>100 kHz, CS <sub>1,2</sub> = 47 nF   |      | 29          |             | μV         |

| VOUT <sub>1</sub> , VOUT <sub>2</sub> RMS Output Noise | VOUT <sub>1,2</sub> = 5 V, I <sub>Load</sub> = 400 mA, 100 Hz to<br>100 kHz, CS <sub>1,2</sub> = 470 nF  |      | 6           |             | μV         |

| EN <sub>1,2</sub> Threshold Voltage                    | OFF                                                                                                      |      |             | 0.5         | V          |

| EN <sub>1,2</sub> Threshold Voltage                    | ON                                                                                                       | 1    |             |             | V          |

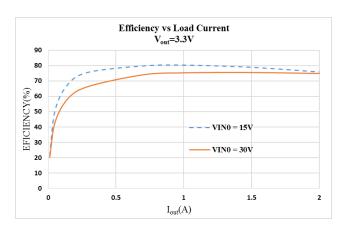

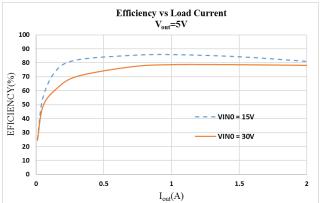

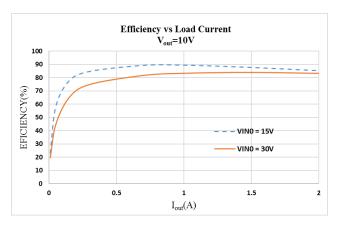

# DC/DC conv. Typical Performance Characteristics

TA = 25° unless otherwise noted

## DC/DC conv. Typical Performance Characteristics

TA = 25° unless otherwise noted

$VIN_0 = 30 \ V$   $VOUT_0 = 5.5 \ V, \ C_{OUT\text{-BK}} = 22 \ \mu\text{F}$   $I_{OUT_0} = 1 \ A, \ f_s = 750 \ k\text{Hz}$

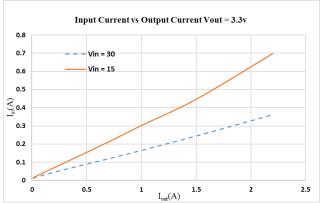

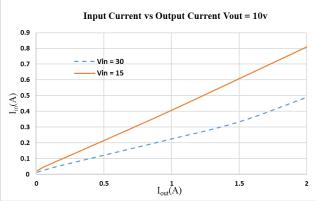

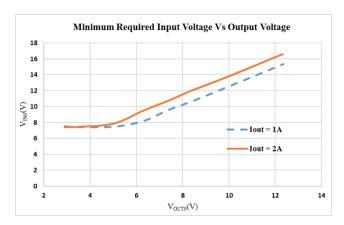

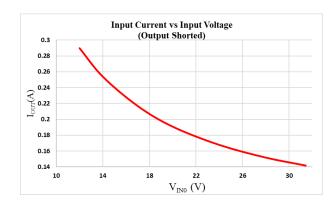

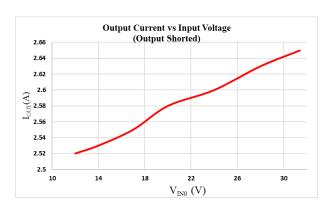

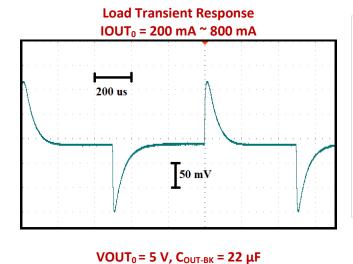

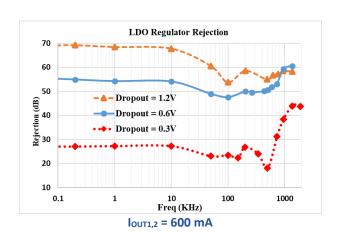

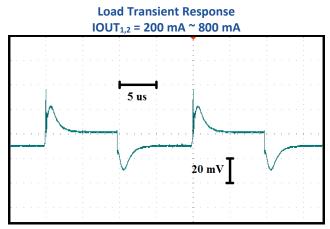

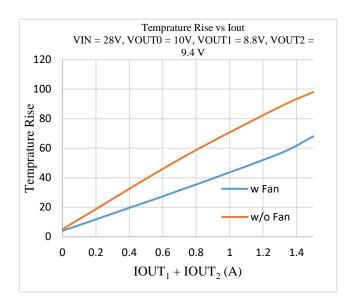

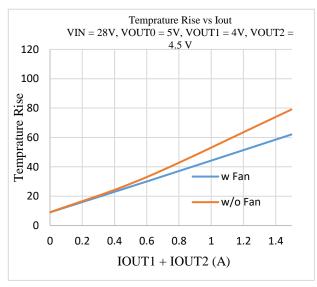

## **LDO Typical Performance Characteristics**

#### TA = 25° unless otherwise noted

**RLIM** is ILIM resistor to VSS

VOUT<sub>0</sub> = 5.6 V VOUT<sub>1,2</sub> = 5 V, C<sub>OUT-LDO</sub> =10 μF l<sub>OUT1,2</sub> = 1 A

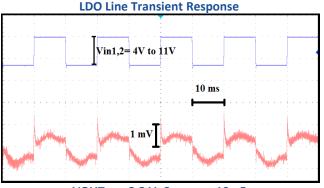

$VOUT_{1,2} = 3.3 \ V, \ C_{OUT\text{-}LDO} = 10 \ \mu F$   $I_{OUT1} = I_{OUT2} = 400 \ mA \ (Buck \ loaded \ with \ LDO)$

$VOUT_0 = 5 \text{ V, } C_{OUT\text{-BK}} = 22 \text{ }\mu\text{F}$   $VOUT_{1,2} = 4 \text{ V, } C_{OUT\text{-LDO}} = 10 \text{ }\mu\text{F}$

## **Pin Functions**

**VSS:** Ground. Tie these pads to local ground plate on PCB. To ensure proper electrical and Thermal performance connect all pins with wide polygon to ground.

**VIN**<sub>0</sub>: The VIN<sub>0</sub> pin supplies current to the ASP2010's internal regulator and to the internal power switch. This pin must be locally bypassed with an external, low ESR capacitor of at least 4.7  $\mu$ F. It's recommended to use low EMI filter before VIN<sub>0</sub> pin as mentioned in application information.

**VX:** DC/DC converter High-side switch drain. This pad should connect to converter Output filter inductor and the Diode Cathode pin in a structure with low electromagnetic emission (refer to PCB Layout recommendation section).

**FB**<sub>0</sub>, **FB**<sub>1</sub>, **FB**<sub>2</sub>: Regulator VOUT feedback. Connect these pads to regulator output node, which want to be regulated. To have a well-regulated voltage use a remote sense connection of this pad to output node. Avoid to near switching tracks to feedback track.

**PG**<sub>0</sub>, **PG**<sub>1</sub>, **PG**<sub>2</sub>: Power-Good Flag. The PG<sub>x</sub> pin is an open-drain logic pin connected to the output of the power good comparator. PG asserts low if output voltage is less than 90% of desired voltage and if output voltage is greater than 90% desired voltage the PG pin de-asserts and becomes high impedance with 24 μs delay. The PG pin may be pulled to 5V or less using a 10 kΩ or more resistor. In LDO regulators fast start ends after PG flag becomes high impedance.

**REF**<sub>1V</sub>: Reference 1 V pad. This pin has a 1 V fixed reference voltage, which makes 100  $\mu$ A fixed current on the 10 k $\Omega$  external connected resistor. This current is mirrored in the chip to generate ADJ<sub>0</sub>, ADJ<sub>1</sub> and ADJ<sub>2</sub> pins current. If another value is used for REF<sub>1V</sub> resistor ADJ0, ADJ1 and ADJ2 pins current will be

$$I_{ADJ} = \frac{1 V}{R_{REF1v}}$$

And regulators' output voltage should be calculated based on this current. Do not connect less than 5  $k\Omega$  resistor to this pin.

ADJ<sub>0</sub>, ADJ<sub>1</sub>, and ADJ2: These pins Adjusts the regulation point for each regulator. For RREF<sub>1V</sub> equal to  $10 \text{ k}\Omega$ , a fixed current of 100 μA flows out of these pins through a single external resistor (R<sub>ADJ0</sub>, R<sub>ADJ1</sub>, R<sub>ADJ2</sub>), which programs the output voltage of each regulator. Output voltage range is from 2V to 12.5V for buck regulator and 0 V to 12 V for LDOs. The required resistor from the formula:

$$R_{ADI} = V_{OUT} \times 2000 \Omega$$

CS<sub>0</sub>, CS<sub>1</sub>, and CS2: These pads control the regulators output voltage soft start speed and output noise spectrum, using a capacitor. LDO regulators have fast start ability. During startup operation and before PG flag become high impedance, a 1 mA current flows out of CS<sub>1</sub> and CS<sub>2</sub> pins and fastens linear regulators output voltage rise speed. Soft start duration is a function of CS capacitor:

$$T_{SOFT-START(BUCK)} = 4 \times 13.2k \times C_{SET0}$$

$$T_{FAST-START(LDO)} = 0.5 \times C_{SET1,2} \times R_{ADJ1,2}$$

**ILIM1,ILIM2:** External Current Limit Programming. This pin externally programs current limit with following function relative to  $R_{LIM}$  ( $k\Omega$ ) resistor connected from this pin to ground:

$$I_{LIM} = 0.8 \frac{R_{LIM}}{5.3 + R_{LIM}} + 0.4 (A)$$

**EN**<sub>0</sub>, **EN**<sub>1</sub>, **EN**<sub>2</sub>: Regulator Enable pin. Each of switching or LDO regulators are enable if relative EN pin voltage level is more than 1 V or disable if voltage level is less than 0.5 V. These pins are internally pull down with 100 kΩ resistor.

**INT\_5V:** This pin is connected to the internal 5 V regulator of the chip with a 2 k $\Omega$  resistor. It can be used to normal enable the buck converter by connecting the EN $_0$  pin to INT\_5V.

## **ASP2010**

### 40 V, 2 A EM Compliant Switching Regulator with 2-Output Configurable LDO

**PAR**<sub>DIS</sub>: LDO Regulator Parallel Disable. This pin externally controls LDO regulators to be in parallel state or independent. Tie this pin to ground to parallel LDO regulators and leave floating for independent operation. PAR<sub>DIS</sub> pin is internally pull up. To parallel two LDO regulators refer to Applications information.

**SYNC:** This is the external clock synchronization input. Tie to a clock source for synchronization. Clock edges rise time and fall time should be faster than 1 $\mu$ s. The internal oscillator of the ASP2010 can be synchronized by applying an external 250 kHz to 2 MHz clock to the SYNC pin. The resistor tied from the RT pin to ground should be chosen such that the ASP2010 oscillates 20% lower than the intended synchronization frequency. Do not leave this pin floating.

**RT:** The RT pin is used to program the switching frequency of the ASP2010 by connecting a resistor from this pin to ground.

| RT (kΩ) | Freq. (kHz) |

|---------|-------------|

| 12      | 2000        |

| 22.5    | 1500        |

| 28      | 1000        |

| 39      | 750         |

| 82      | 375         |

| 125     | 250         |

**VOUT<sub>1</sub>, VOUT<sub>2</sub>:** LDO Output. These pins supply power to the load. Connect VOUT<sub>1</sub> and VOUT<sub>2</sub> pins together In Parallel Mode. Stability requirements demand 10 μF ceramic output capacitor with an ESR less than  $100 \, \text{m}\Omega$  to prevent oscillations.

**TH\_SHDN:** Thermal shutdown flag. This pin generates the 5 V thermal shutdown signal when the chip temperature reaches 185 °C. in addition, TH\_SHDN flag disables all regulators and enables them again when the chip temperature decreases to 165 °C. this pin can be tied to VSS if user does not need thermal shutdown reaction.

**SET, STRB, DIN, CLK:** These pins are used for productions tests. Tie these pins to VSS.

# **ASP2010**

## 40 V, 2 A EM Compliant Switching Regulator with 2-Output Configurable LDO

|                  |       |           | <u> </u>                  |                           |                           |                           |                           |

|------------------|-------|-----------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| VIN <sub>0</sub> | VOUT₀ | Соит      | R <sub>ADJ0</sub><br>(kΩ) | f <sub>opt</sub><br>(kHz) | RT <sub>opt</sub><br>(kΩ) | f <sub>MAX</sub><br>(kHz) | RT <sub>MIN</sub><br>(KΩ) |

| 8V ~ 35V         | 1.50V | 22μF 1206 | 3                         | 400                       | 50                        | 700                       | 43                        |

| 8V ~ 35V         | 2.5V  | 22μF 1206 | 5                         | 600                       | 75                        | 900                       | 33                        |

| 8V ~ 15V         | 3.5V  | 22μF 1206 | 7                         | 850                       | 35                        | 100                       | 33                        |

| 15V ~ 35V        | 3.5V  | 22μF 1206 | 7                         | 750                       | 40                        | 900                       | 30                        |

| 8V ~ 35V         | 4.5V  | 22μF 1206 | 9                         | 850                       | 35                        | 1000                      | 30                        |

| 8V ~ 20V         | 5.5   | 22μF 1206 | 11                        | 1000                      | 30                        | 1200                      | 25                        |

| 20V ~ 35V        | 5.5   | 22μF 1206 | 11                        | 900                       | 33                        | 1100                      | 27                        |

| 8V ~ 15V         | 6.5   | 22μF 1206 | 13                        | 950                       | 32                        | 1200                      | 25                        |

| 15V ~ 35V        | 6.5   | 22μF 1206 | 13                        | 850                       | 35                        | 1000                      | 30                        |

| 10V ~ 15V        | 7.5   | 22μF 1206 | 15                        | 1000                      | 30                        | 1200                      | 25                        |

| 15V ~ 35V        | 7.5   | 22μF 1206 | 15                        | 850                       | 35                        | 1100                      | 27                        |

| 12V ~ 20V        | 8.5   | 22μF 1206 | 17                        | 1100                      | 27                        | 1200                      | 25                        |

| 20V ~ 35V        | 8.5   | 22μF 1206 | 17                        | 900                       | 33                        | 1100                      | 27                        |

| 12V ~ 20V        | 10    | 22μF 1206 | 20                        | 1200                      | 25                        | 1200                      | 25                        |

| 20V ~ 35V        | 10    | 22μF 1206 | 20                        | 950                       | 32                        | 1100                      | 27                        |

### **Typical Applications**

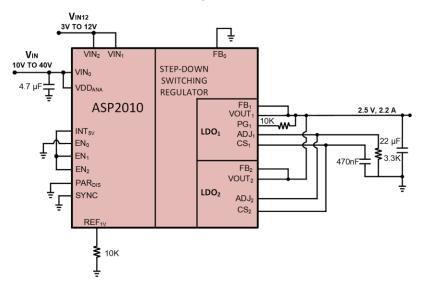

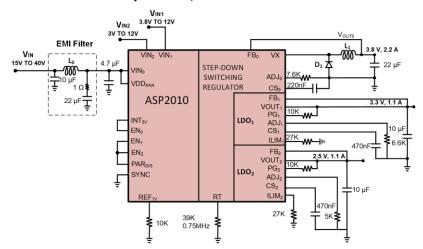

## LDOs Parallel, Buck Disable

### **LDOs Independent, Not Connected to Buck**

## LDOs Independent, Buck Disable

## **Application Information**

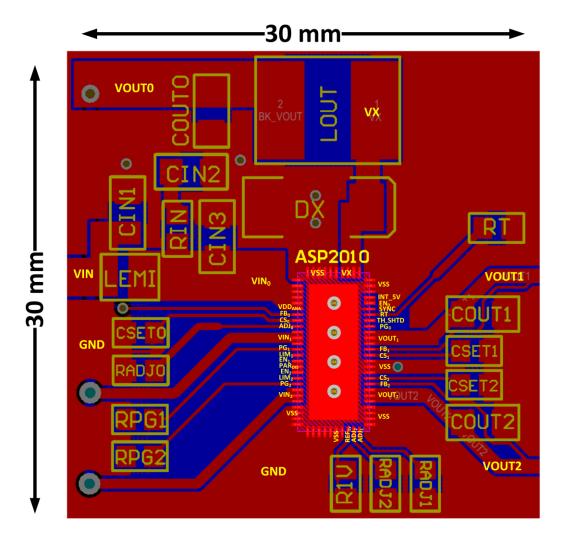

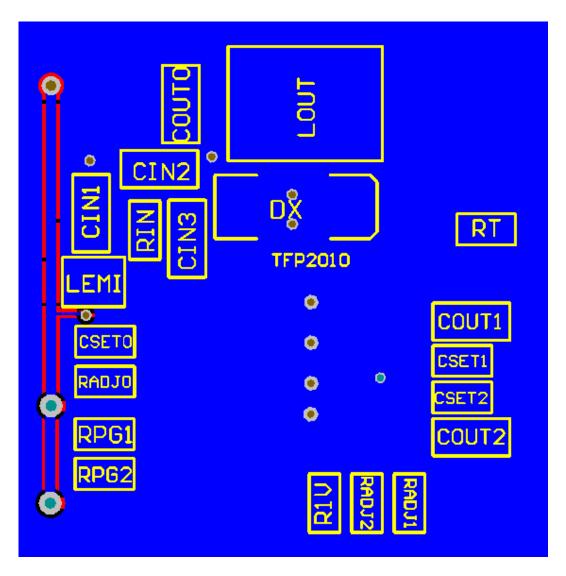

#### **PCB Layout**

The ASP2010 includes a switching power supply and care must be taken to minimize EMI and ensure proper operation. Even with the high level of integration, you may fail to achieve specified 5. operation with a haphazard or poor layout. See Figure 3 for a suggested layout. Ensure that the grounding and heat sinking are acceptable. A few rules to keep in mind are:

- possible to their respective pins.

- 2. Place the C<sub>IN</sub> capacitor as close as possible to the VIN and GND connection of the ASP2010.

- 3. Place  $C_{\text{OUT}}$  capacitors as close as possible to relative VOUT and GND connection of the ASP2010.

- Place the C<sub>IN</sub> and C<sub>OUT</sub> capacitors such that their ground currents flow directly adjacent or underneath the ASP2010.

- Connect all of the GND connections to as large a copper pour or plane area as possible on the top layer. Avoid breaking the ground connection between the external components and the ASP2010.

- 1. Place the R<sub>ADJ</sub> and RT resistors as close as 6. Use vias to connect the GND copper area to the board's internal ground plane. Liberally distribute these GND vias to provide both a good ground connection and thermal path to the internal planes of the printed circuit board.

**Top View**

**Bottom View**

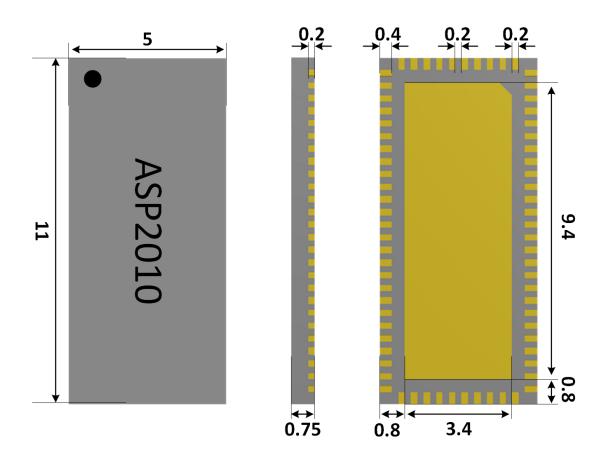

# All dimensions are in mm ± 0.05 mm

72 pin QFN Package

## **Recommended Off-chip Components**

| Component             | Value          | Manufacturer | Recommended Part Number |

|-----------------------|----------------|--------------|-------------------------|

| 0                     |                | ONSEMI       | MBRS360BT3G             |

| <b>D</b> <sub>1</sub> | D <sub>1</sub> | ST           | STPS3H60-Y              |

| •                     | 47             | Coil Craft   | XAL5030-472ME           |

| L <sub>1</sub>        | 4.7 μΗ         | Coil Craft   | XGL6030-472ME           |

| L <sub>0</sub>        | 4.7 μΗ         | TDK          | 252012ALMA4R7MTAA       |